Advanced Packaging Market Size to Reach USD 103.69 Billion by 2032, Growing at 11.5% CAGR on AI Chiplets and HPC Demand

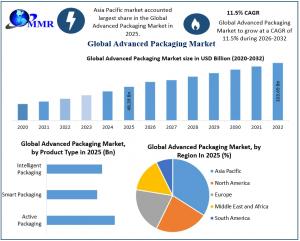

Advanced Packaging Market valued at USD 48.39 Billion in 2025, projected to reach USD 103.69 Billion by 2032 at an 11.5% CAGR.

Advanced packaging is the new Moore’s Law; Maximize Market Research predicts a USD 103.69 billion shift in semiconductor sovereignty.”

ROCKVILLE , MD, UNITED STATES, March 23, 2026 /EINPresswire.com/ -- The global semiconductor landscape is witnessing a seismic shift as the Advanced Packaging Market, valued at USD 48.39 Billion in 2025, is projected to surge to USD 103.69 Billion by 2032. According to a comprehensive analysis by Maximize Market Research, this industry is set to expand at a CAGR of 11.5% from 2026 to 2032. As Moore’s Law encounters physical limitations, high-performance computing (HPC) and Generative AI are driving the adoption of chiplet-based architectures and 2.5D/3D IC stacking, cementing advanced packaging as the new frontier for silicon innovation and global supply chain sovereignty.— Maximize Market Research

Get Full PDF Sample Copy of Report: (Including Full TOC, List of Tables & Figures, Chart) @ https://www.maximizemarketresearch.com/request-sample/30807/

Beyond Moore’s Law: How Heterogeneous Integration and AI Demand are Scaling the Advanced Packaging Ecosystem Through 2032

The transition from traditional monolithic die designs to heterogeneous integration is reshaping the global semiconductor ecosystem. As the industry pivots toward the 'More-than-Moore' era, advanced packaging has evolved from a back-end protective process into a front-end performance differentiator. A prime real-world example is NVIDIA’s Blackwell GPU architecture, which utilizes TSMC’s CoWoS technology to link logic and high-bandwidth memory. This shift is primarily driven by the demand for energy-efficient processors in AI data centers and automotive electronics. By enabling higher interconnect density, these solutions allow manufacturers to overcome physical scaling limits, ensuring next-generation infrastructure can meet massive computational workloads.

Advanced Packaging Market Segmentation: 2.5D/3D Stacking and Chiplets Emerge as the USD 100 Billion Growth Engine

The Advanced Packaging Market is strategically categorized by technology, including Flip-Chip, Fan-Out Wafer-Level Packaging (FOWLP), and 2.5D/3D IC Stacking. Currently, the 2.5D/3D segment is the primary growth catalyst, essential for integrating High-Bandwidth Memory (HBM3E) with AI accelerators. This segment is projected to witness the highest CAGR as foundries like TSMC and Samsung scale CoWoS and I-Cube capacities to meet hyperscaler demands.

In terms of end-use, Consumer Electronics continues to hold the largest volume share, driven by the shift toward 5G-enabled miniaturized devices. However, the Automotive & EV sector is the fastest-expanding vertical. This acceleration is fueled by the transition to 800V architectures and Autonomous Driving (ADAS), which require ruggedized, high-performance packaging such as Power Modules and System-in-Package (SiP). By 2032, these specialized segments will be instrumental in reaching the USD 103.69 Billion market valuation, as disaggregated chiplet designs become the industry standard.

By Product Type

Active Packaging

Smart Packaging

Intelligent Packaging

By Packaging Type

3D Integrated Circuit

Fan Out Silicon in Package

Fan Out Wafer Lever Package

3D Wafer Level Package

Wafer Level Chip Scale Package

2.5D

Flip Chip

By Industrial Vertical

Consumer Electronics

IT & Telecommunication

Automotive & Transport

Healthcare

Aerospace & Defense

Others

Get Full PDF Sample Copy of Report: (Including Full TOC, List of Tables & Figures, Chart) @ https://www.maximizemarketresearch.com/request-sample/30807/

Regional Insights: Asia-Pacific Commands 65% Market Share as North America’s "Reshoring" Strategy Targets 10% CAGR through 2032

The Asia-Pacific region continues to dominate the advanced packaging landscape, commanding over 65% of global revenue in 2025. This leadership is anchored by the specialized "foundry-to-OSAT" clusters in Taiwan, South Korea, and China, where high-volume production of HBM3E and FOWLP remains concentrated. However, North America is projected as the fastest-growing market through 2032. This surge is fueled by over USD 50 Billion in federal CHIPS Act incentives, driving a strategic pivot toward domestic high-end assembly. By localizing 2.5D/3D integration for AI-centric data centers, the U.S. aims to reduce offshore dependency and ensure semiconductor supply chain resilience.

Strategic Growth Catalysts: The AI "Memory Wall" and 3D Stacking Challenges Reshaping Semiconductor Integration

The demand for advanced chip packaging is propelled by the explosive growth of Generative AI accelerators and High-Performance Computing (HPC). A defining real-world example is NVIDIA’s Blackwell GPU, which utilizes TSMC’s CoWoS technology to overcome the "Memory Wall"—the bottleneck where data cannot move fast enough between the processor and High-Bandwidth Memory (HBM3E). Conversely, the industry faces a significant restraint in High Capital Intensity. Establishing a single 3D IC stacking or panel-level packaging (PLP) line now requires investments exceeding USD 500 million. Furthermore, the complexity of chiplet-based architectures often leads to lower initial manufacturing yields, challenging the cost-efficiency of smaller semiconductor players.

The Chiplet Revolution: Modular Architectures and UCIe Standardization Driving System-in-Package Innovation

The industry is pivoting from monolithic silicon to disaggregated chiplet-based architectures, a move essential for sustaining performance gains as transistor scaling slows. A standout real-world example is the AMD Instinct MI300 series, which utilizes advanced 3D stacking to integrate CPU and GPU chiplets with HBM3 memory in a single modular package. This "LEGO-like" approach allows manufacturers to combine different process nodes—using expensive 3nm for compute and cost-effective 7nm for I/O—optimizing both yield and performance.

A critical 2026 trend fueling this shift is the broad adoption of the Universal Chiplet Interconnect Express (UCIe) standard. By providing a "common language" for dies from different vendors to communicate, UCIe is transforming the Advanced Packaging Market into a modular ecosystem. This standardization, combined with innovations like Hybrid Bonding and Glass Substrates, is the technological backbone required to reach the USD 103.69 Billion valuation by 2032.

Thermal Bottlenecks: Overcoming the 1000W Power Limit in Next-Generation 3D IC Architectures

As the semiconductor assembly industry moves toward vertical 3D stacking, localized heat density has become the ultimate performance bottleneck. Traditional conduction-based cooling is hitting physical limits, as stacked dies trap heat far from the primary heat sink. A significant industry response is the partnership between Intel and CoolIT Systems, which integrates direct-to-chip liquid cooling to manage thermal loads exceeding 1000W. By adopting microfluidic cooling and advanced Thermal Interface Materials (TIM1.5), manufacturers are mitigating the "hotspot amplification" that threatens chip reliability. These thermal innovations are essential to maintaining the performance gains required for 2032’s billion-dollar market projections.

Competitive Landscape: The Rise of the "System Foundry" and the Convergence of Foundries and OSATs

The competitive environment is defined by an intensifying rivalry between traditional OSATs (Outsourced Semiconductor Assembly and Test) and major Foundries. While ASE Technology Holding and Amkor maintain dominance in high-volume assembly, TSMC and Intel are disrupting the market by internalizing advanced processes like CoWoS and Foveros. A landmark development is the TSMC-Amkor partnership in Arizona, designed to create a turnkey ecosystem for US-based AI chip production. This shift toward a "System Foundry" model where silicon fabrication and advanced packaging are bundled is forcing consolidation as players like Samsung and JCET race to offer integrated 2.5D/3D solutions to hyperscale customers.

Advanced Packaging Market, Key Players

1.ASE Group

2.Amkor Technology

3.STATS ChipPAC Pte. Ltd.

4.SSS MicroTec AG.

5.IBM

6.Intel Corporation

7.Qualcomm Technologies

8.Chipbond Technology Corporation

9.Samsung Electronics Co. Ltd

10.Texas Instruments

11.Analog Devices

12.Microchip Technology

13.TSMC

14.Deca Technologies

15.Sanmina Corporation

Get access to the full description of the report @ https://www.maximizemarketresearch.com/market-report/global-advanced-packaging-market/30807/

Analyst Perspective

The shift toward advanced semiconductor integration is no longer a luxury but a survival mandate for the AI era," states a Senior Analyst at Maximize Market Research. "As we approach a USD 103.69 Billion market by 2032, the focus is transitioning from mere miniaturization to Heterogeneous Integration. The real-world success of NVIDIA's Blackwell architecture proves that the winner of the semiconductor race will be decided in the packaging house, not just the fabrication plant. Companies that successfully bridge the 'Thermal Wall' using Liquid Cooling and Glass Substrates will capture the lion's share of this 11.5% CAGR growth.

FAQ’s

What is the projected size of the Advanced Packaging Market by 2032?

Ans: The global market is expected to reach USD 103.69 Billion by 2032, growing at a 11.5% CAGR. This surge is fueled by high-performance computing and Generative AI demands.

Which technology is driving growth in semiconductor assembly?

Ans: 2.5D and 3D IC stacking are the primary catalysts, essential for integrating HBM3E memory in AI accelerators like NVIDIA’s Blackwell.

What is the biggest challenge in high-density packaging?

Ans: Thermal management is the critical bottleneck. Industry leaders are adopting liquid cooling and microfluidics to manage heat loads exceeding 1000W in stacked architectures.

Related Reports

Semiconductor Gas Filter market: https://www.maximizemarketresearch.com/market-report/semiconductor-gas-filter-market/268613/

Semiconductor Wafer Inspection Equipment Market: https://www.maximizemarketresearch.com/market-report/semiconductor-wafer-inspection-equipment-market/249366/

Semiconductor Gases Market: https://www.maximizemarketresearch.com/market-report/semiconductor-gases-market/243111/

Semiconductor Devices Market: https://www.maximizemarketresearch.com/market-report/semiconductor-devices-market/243104/

Wafer Processing Equipment Market: https://www.maximizemarketresearch.com/market-report/wafer-processing-equipment-market/172780/

Top Reports:

Microfluidics Market

Global Telemedicine Market

About Maximize Market Research

Maximize Market Research is a leading global market research and business consulting firm. Our revenue-impact and growth-driven initiatives empower Fortune 500 companies to navigate complex industrial shifts and secure high-value market dominance.

Domain Focus: Information Technology & Telecommunication

Our research evaluates the convergence of 2.5D/3D IC stacking and heterogeneous integration. We analyze the lifecycle economics of chiplet-based architectures, from UCIe-standardized interconnects to the AI-integrated supply chains redefining global semiconductor throughput and computing efficiency.

Lumawant Godage

MAXIMIZE MARKET RESEARCH PVT. LTD.

+ +91 96073 65656

email us here

Visit us on social media:

LinkedIn

Instagram

Facebook

X

Legal Disclaimer:

EIN Presswire provides this news content "as is" without warranty of any kind. We do not accept any responsibility or liability for the accuracy, content, images, videos, licenses, completeness, legality, or reliability of the information contained in this article. If you have any complaints or copyright issues related to this article, kindly contact the author above.